#### Der Bus als Kommunikationsmedium

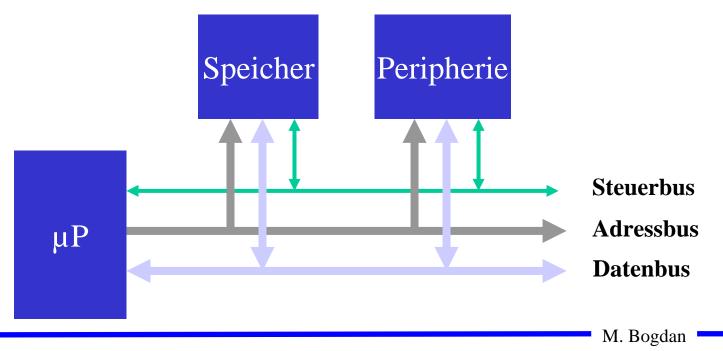

- O Bus ist eine Sammelleitung zur Übertragung von Daten zwischen mehreren Funktionseinheiten einer Rechenanlage

- O Es muss dafür gesorgt werden, dass

- ⇒ verschiedene Geräte nicht gleichzeitig Daten senden

- Bus Arbitrierung

- ⇒ nur solche Geräte die Daten empfangen, für die sie bestimmt sind

- Bus Protokoll

- O Ein Bus besteht in der Regel aus

- **Datenleitungen**

- **⇒** Adressleitungen

- **⇒** Steuerleitungen

#### Rechner- und Gerätebusse

- O Busse verbinden Komponenten eines Rechnersystems

- **⇒** Datenbus 8 bis 64 Bit

- **⇒** Adressbus 16 bis 64 Bit

- **⇒** Steuerbus

- Systembusse

- **⇒** Busse, die rechnerinterne Komponenten verbinden

- **⇒ AT-Bus PC/XT** (8088/ 8086)

- **⇒ ISA-Bus AT (80286)**

- **⇒ EISA** 80386 und 80486

- **⇒ VESA ab 80486**

- ⇒ PCI ab 80486 bis Pentium4

- Gerätebusse

- **⇒** Busse, die externe Komponenten mit einem Rechnersystem verbinden

- **⇒ IEC** Gerätebus

- **⇒ EIDE** Festplatten

- **⇒ SCSI** Geräte und Festplattenbus

# **Systembusse**

- **○** Verbindung der Komponenten innerhalb eines Rechnersystems

- Prozessorabhängige Busse

- **⇒** Busschnittstelle des verwendeten Mikroprozessors

- ⇒ einfach zu realisieren

- **⇒** auf einen Prozessor zugeschnitten

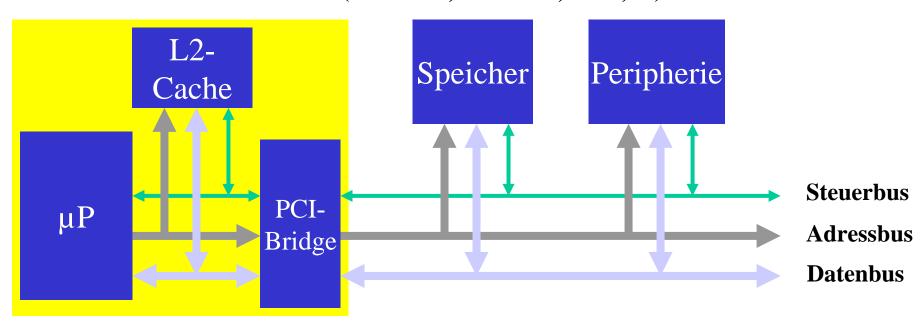

## Prozessorunabhängige Systembusse

- O Der Prozessor ist über eine Bus Brücke mit den Komponenten verbunden

- ⇒ z.B. PCI Bridge (Peripheral Component Interconnect)

- ⇒ erhöhter Hardwareaufwand

- ⇒ die Komponenten können für verschiedene Prozessoren verwendet werden (PPC 403, Pentium, I860, ...)

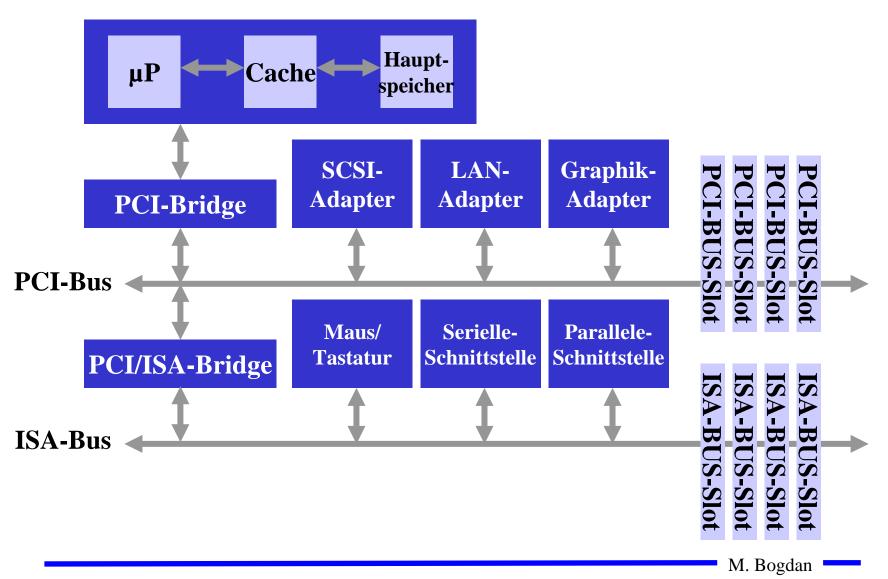

# Beispiel: Busstruktur eines PC

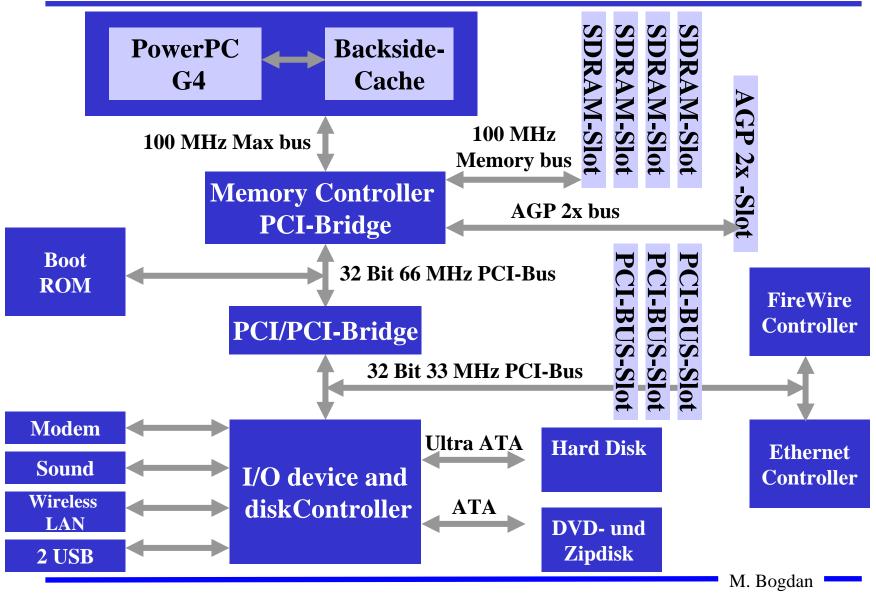

## Beispiel: Busstruktur des Power Mac G4

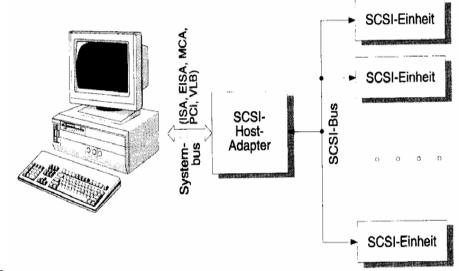

### Gerätebusse: Der SCSI-Bus

- Small Computer Systems Interface

- **⇒** Maximal 8 Einheiten

- **⇒** 8 Bit Übertragung

- **⇒** Identifikation durch SCSI-ID

- ⇒ Terminierung durch Abschlußwiderstand

- Weitere SCSI-Standards

- **⇒** SCSI-II

- Erster richtiger Standard, der am gleichen Bus auch andere Geräte außer Festplatten berücksichtigt

- **⇒** Fast SCSI

- maximale Taktfrequenz wurde auf 10 MHz erhöht

- **⇒** Wide SCSI

- 16 Bit und 32 Bit Erweiterung der Datenbreite

# Aufbau von Speicherzellen

- Speicherung von Daten oder von logischen Funktionen

- Arten der Speicherung

- ⇒ irreversibel programmierbare Speicherzellen

- ⇒ reversibel programmierbare Speicherzellen

- ⇒ spezielle

Transistorschaltungen als

statisches Speicherelement

- **⇒** Speicherung der Daten in einem Kondensator

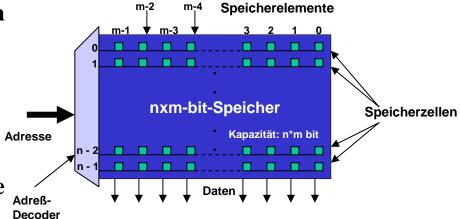

- O Speicherung der kleinsten Informationseinheit (Bit) in einem Speicherelement

- Speicherzelle

- ⇒ Speicherelemente, die unter einer gemeinsamen Adresse ansprechbar sind

- Speicherwort

- **Datenbusbreite**

- Organisation

- **⇒** Anzahl der Speicherzellen

- **⇒** Anzahl der Speicherelemente

- ⇒ n\*m Bit

- Kapazität

- **⇒** Zahl der Speicherelemente

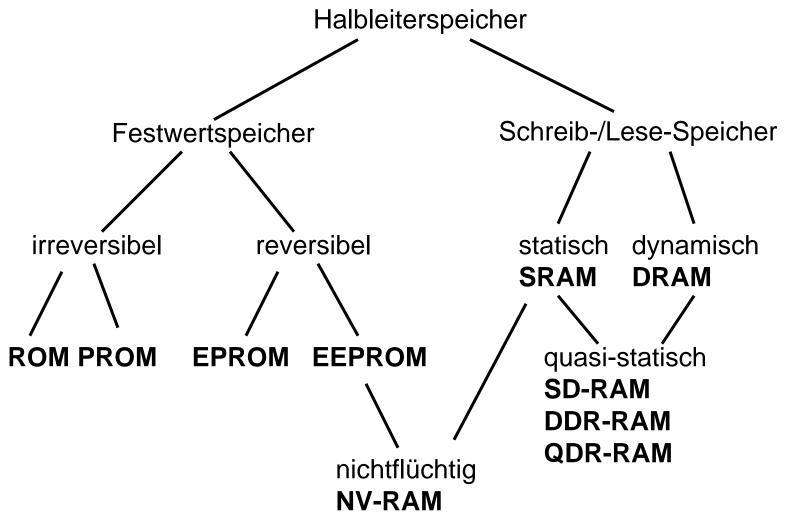

# Klassifizierung von Halbleiterspeichern

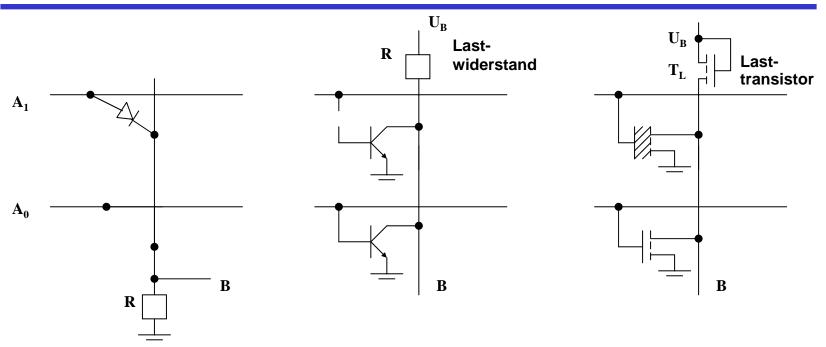

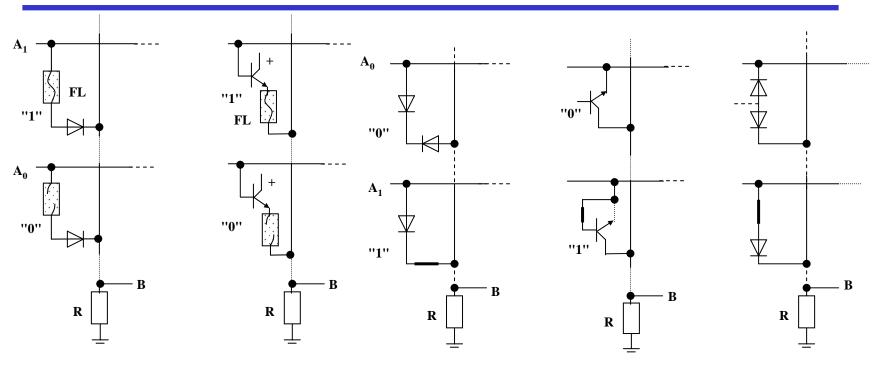

## Speicherzellen für maskenprogrammierbare Speicherelemente

- Maskenprogrammierbare Speicherelemente erhalten ihre Information bei der Herstellung des Chips

- **⇒** Information steht auf einer der Masken

- **⇒** Inhalt ist nicht veränderbar

- O Bauelemente wie Dioden, Bipolar- oder MOS-Transistoren werden bei der Herstellung deaktiviert

- ⇒ Bei MOS-Transistoren ist die Dicke der Gate-Isolation ausschlaggebend

## Speicherzellen für programmierbare Speicherelemente

Speicherzellen mit Schmelzsicherungen

**AIM-Speicherzellen**

- O Programmierung in Programmiergerät durch Überspannungen

- **⇒** Schmelzsicherung

- **⇒** Zerstören von Dioden (dauernd leitend)

- O Information ist nur einmal schreibbar und kann nicht verändert werden

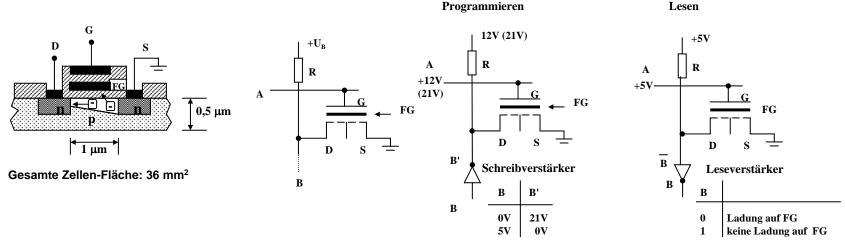

# Löschbare Speicherelemente

- O Löschen durch UV-Licht

- **O** FAMOS: floating gate avalance MOS-transisistor

- ⇒ Besitzt zweites Gate, das vollständig isoliert ist

- ⇒ Speicherung der Ladung über 30 Jahre

- O Programmierung durch hohe Spannung (12-21 V)

- **⇒** Elektronen werden angezogen

- Programmieren und Lesen einer EPROM-Zelle

- Lesen durch Anlegen einer niederen Spannung (5 V)

- ⇒ ist das Floating-Gate geladen, schaltet der Transistor nicht

## Elektrisch löschbare Speicherelemente

- **O Dünne Isolierschicht des Floating Gates**

- ⇒ Lesen: Wenn das Floating Gate des Transistors geladen ist, sperrt dieser

- $\Rightarrow$  Löschen: Hohe Spannung (21 V) am Gate-Anschluß des Transistors lädt das Floating Gate ( $U_B = 0V$ )

- ⇒ Programmieren: 0 V am Gate und eine hohe Spannung am Drain-Anschluß des Transistors entlädt einzelne Floating Gates (logisch 0)

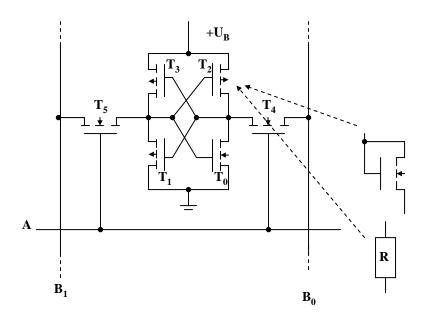

# **Statische MOS-Speicherelemente**

- **○** 6-Transistorzelle

- ⇒ Statt T<sub>2</sub> und T<sub>3</sub> können auch n-MOS-Transistoren oder Widerstände eingesetzt werden

- ⇒ T<sub>4</sub> und T<sub>5</sub> dienen zur Ankopplung an die Bitleitungen

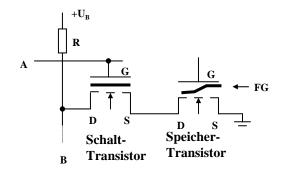

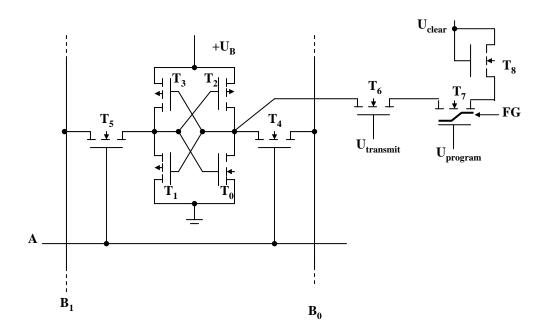

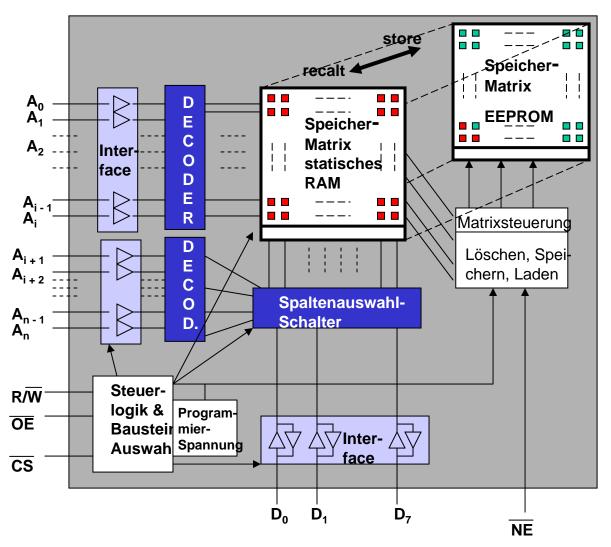

# **NVRAM-Speicherelemente**

- O Kombination eines statischen mit einem EEPROM Speicherelement

- ⇒ wenn die Spannung abfällt oder das Gerät eingeschaltet wird, findet eine Übertragung von bzw. in die EEPROM-Zelle statt

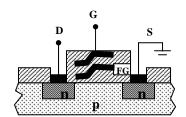

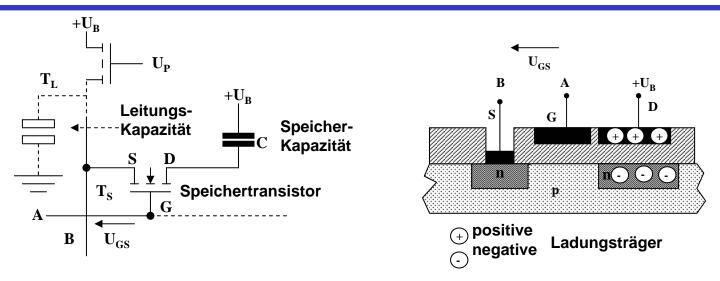

## **Dynamische Speicherelemente**

- O Die Information wird in einem Kondensator gespeichert

- ⇒ vergrößerte Drain-Zone

- **⇒** isoliert zur Spannungsversorgung

- O Kapazität 0,1 bis 0,5 pF, 100.000 bis 150.000 Elektronen

- ⇒ Selbstentladung nach ca. 2 ms

- O Speichern entspricht dem Laden des Kondensators

- Lesen entlädt den Kondensator

- **⇒** Daten müssen wieder zurückgeschrieben werden

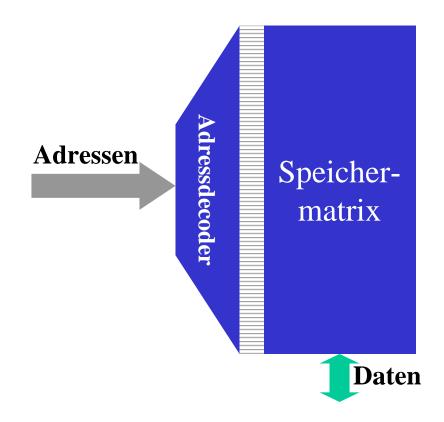

# **Äußere Organisation**

- Organisation des Speicherbausteins als Wortbreite und Adressbereich

- O Beispiele: 512k\*8, 4M\*1

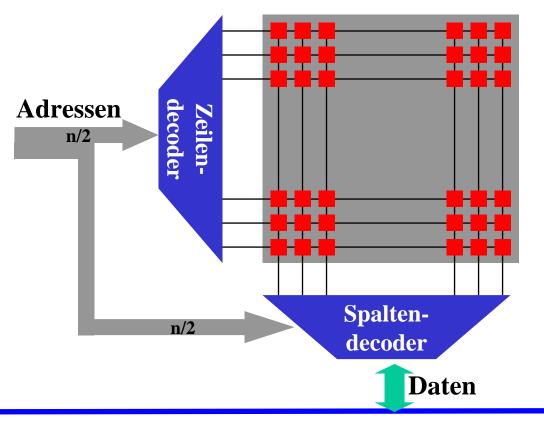

# **Innere Organisation**

- O Anordnung der Speicherzellen in einer quadratischen Matrix

- ⇒ ergibt die minimale Anzahl der Ansteuerleitungen

- O Aus den 2<sup>n/2</sup> Datenbits werden im Spaltendecoder m Bits ausgewählt

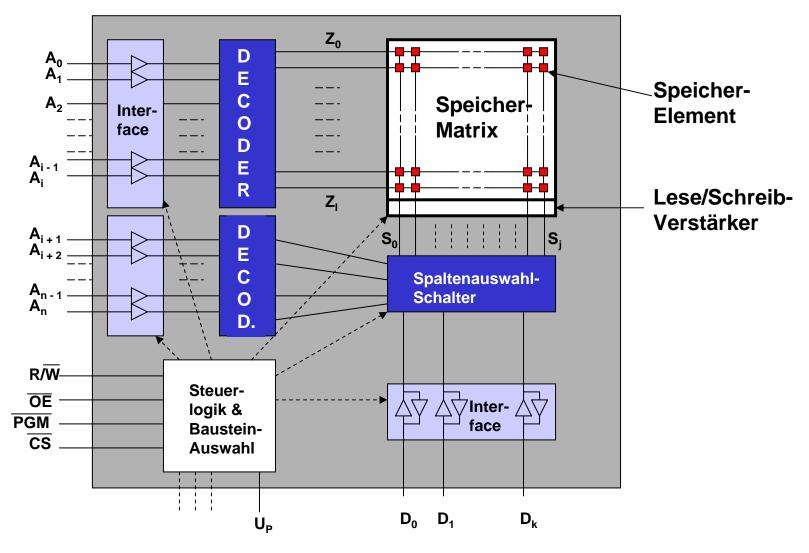

# Aufbau eines Speicherbausteins

## **NVRAM-Bausteine**

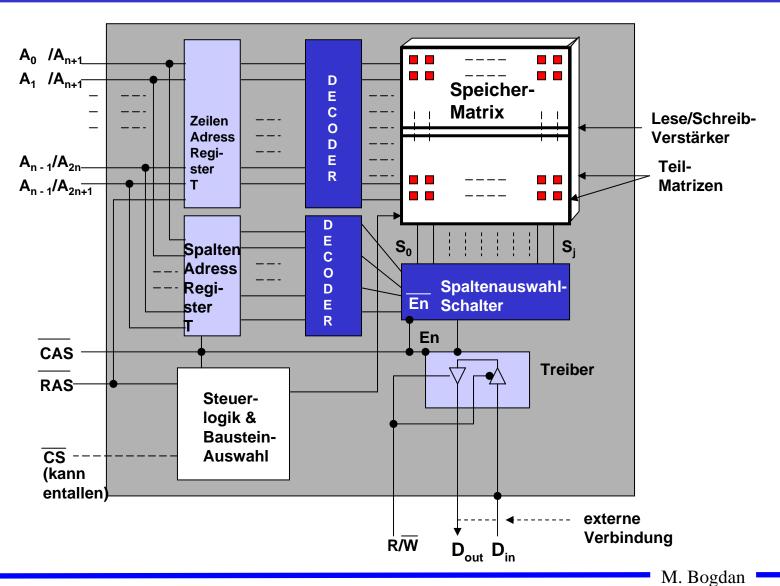

# **Dynamische RAM-Bausteine**

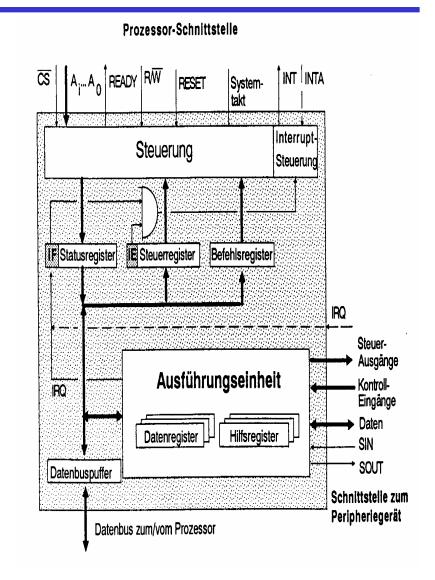

# 10 E/A und Peripheriegeräte

- Ein- und Ausgabe erfolgt über spezielle Speicherstellen im Adressraum des Prozessors

- **⇒** Memory Mapped

- **⇒** spezielle I/O-Befehle

- Adressdekodierung erzeugt das CS-Signal (chip select)

- Der Prozessor kommuniziert über

- **⇒** Datenregister (Lesen und Schreiben der Daten)

- **⇒** Statusregister (Zustand des Bausteins)

- ⇒ Steuerregister (Betriebsart des Bausteins)

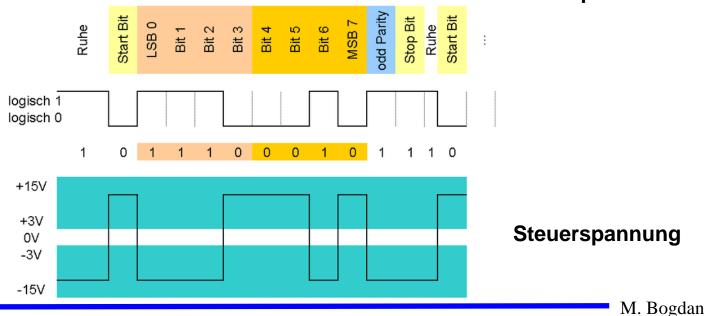

### Serielle Schnittstelle: RS232

#### O Synchronisation über den Aufbau des Datenworts

**⇒** Start: Startbit

**⇒ 1,...,n:** 5 bis 8 Datenbits

⇒ P: Parität

⇒ Stopp: 1, 1.5 oder 2 Stoppbits

Syncronisation

Daten low & high

Check

9600 8O1 = 9600 Baud; 8 Datenbits; odd Parity; 1 Stopbit

ASCII "G" = \$47 = 0100 0111

Beispiel: EIA 232 (RS232)

### Die RS232-Schnittstelle

- **O** RTS: request to send

- **⇒** Sendeteil einschalten

- O CTS: clear to send

- **⇒** Übertragungseinrichtung sendebereit

- O DCD: data carrier detect

- **⇒** Trägersignal erkannt

- **⇒** Empfangsteil einschalten

- O DSR: data set ready

- **⇒** Übertragungseinrichtung betriebsbereit

- O DTR: data terminal ready

- **⇒** Empfangseinrichtung betriebsbereit

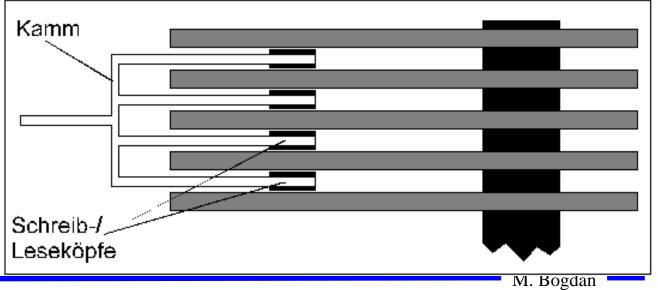

# Aufbau eines Festplatten-Laufwerks

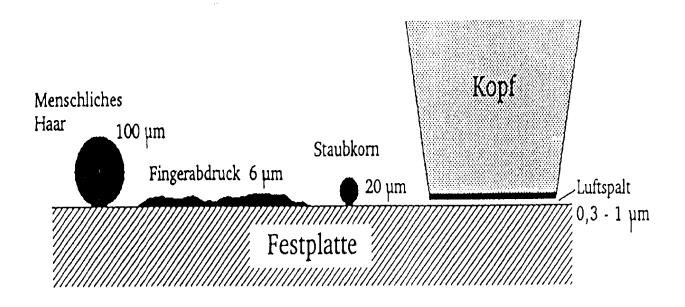

# Größenverhältnisse im Festplatten-Laufwerk

Größenvergleich

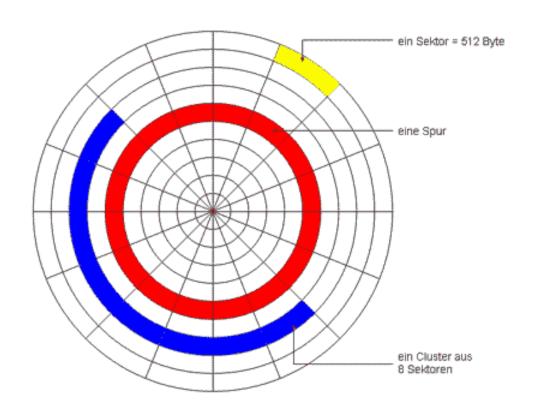

# Sektoren einer Festplatte

- O Sektor: 512 Byte

- O Spur: "Lesestreifen"

- ⇒ Sektoren auf äußeren Spuren sind flächenmäßig größer

- **⇒ Trotzdem 512 Byte!**

- O Cluster: Verbund von Sektoren; Größe abhängig von der Partitionierung

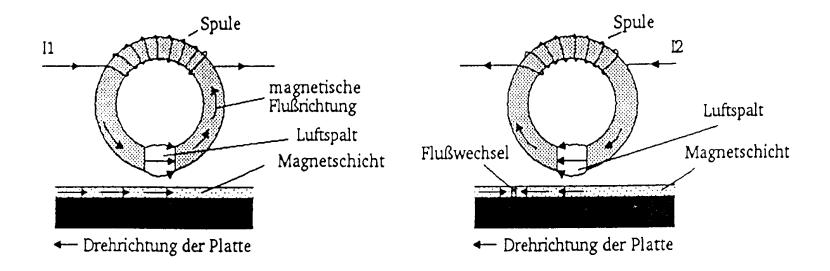

# Prinzip der Datenspeicherung

- O Das Prinzip der Datenaufzeichnung besteht darin, die Oberfläche der Platte informationsabhängig zu magnetisieren.

- Zur Unterscheidung der "0"- und "1"-Bits wird die Richtung der Magnetisierung verändert. Jede Änderung der Magnetisierungsrichtung wird als flusswechsel bezeichnet.

# Zusammenfassung

#### O TI1

- **⇒** Elektrotechnische Grundlagen

- Einfache physikalische Zusammenhänge, die verwendet werden um Schaltvorgänge in Rechnersystemen durchzuführen

- **⇒** Halbleitertechnologie

- Funktionsweise von Dioden und Transistoren

- Einsatz von Transistoren als Schalter

- CMOS-Schaltungen

- **⇒** Digitale Grundlagen

- Entwurf und Darstellung von Schaltnetzen

# Zusammenfassung

#### O TI2

- **⇒** Digitaltechnik

- Optimierung von Schaltnetzen und Schaltwerken

- **⇒** Komponenten digitaler Systeme

- Funktion und Aufbau komplexer Bausteine

- Komponenten aus denen Rechnersysteme aufgebaut sind

- **⇒** Rechnerarithmetik

- Darstellung von Zahlen und Zeichen in Rechnersystemen

- Algorithmen zur Berechnung von Operationen wie die vier Grundrechenarten

- **⇒** Aufbau und Funktionsweise einfacher Rechnersysteme

- Komponenten

- Busse

- Speicher

- Peripherie